# x86: Initialization & Devices

Gabriel Laskar <gabriel@lse.epita.fr>

# x86 power on

- Chips self initialize

- Cpu initialization

- Firmware starting

- Boot code launch OS

- Execute the CPU reset vector (4Gb 16b):

0xfffffff0.

- This address is in the BIOS/UEFI flash memory.

- CPU initialization

- platform firmware switch to the firmware mode (real, voodooo or flat protected)

- Preparation for memory initialization

- CPU microcode update

- CPU specific initialization

- need to setup some kind of stack, before RAM initialization, for that cache-as-RAM is used (CAR)

- some CPUs need to initialize some specific MSRs

- Chipset initialization : BAR is initialized, watchdog is disabled

- RAM Initialization

- Relocate firmware code in RAM

- Memory Test

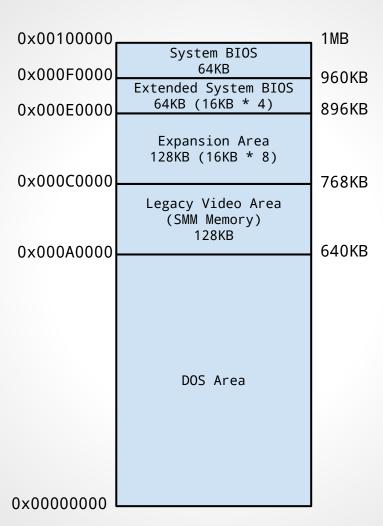

- BIOS Shadowing

- Redirect memory transactions

- Set up the stack

- transfer firmware to ram

- Misc platform enabling (clock, gpio)

- IRQ enabling and IRQ chips initialization

- Timer initialization

- Memory cache control initialization

- APs initialization (MTRRs must be consistent across all cores)

- Simple IO Device initialization (ps/2, serial)

- PCI Device discovery and initialization

- OS boot loader execution

#### **BIOS**

- 16-bit code

- old, ancient way

- boot MBR partitions (0x55aa)

- user-api is interrupts

# **BIOS Interrupts**

- int \$0x10 : Video Services

- int \$0x11 : Equipment list

- int \$0x12 : lowmem size

- int \$0x13 : Disk Services

- int \$0x14 : Serial port Services

- int \$0x15 : Misc services (0xe820, ...)

- ...

#### **UEFI**

- 32 or 64 bit code

- New "modern" way

- New partition format

- Interface based api

# Example

```

#include <efi.h>

EFI_STATUS main(EFI_HANDLE ImageHandle,

EFI_SYSTEM_TABLE *SystemTable)

SystemTable->ConOut->Outputstring(

SystemTable->ConOut, L"Hello World\r\n");

return EFI_SUCCESS;

```

# **Different types of Applications**

- Applications

- Boot services

- Runtime services

- Drivers

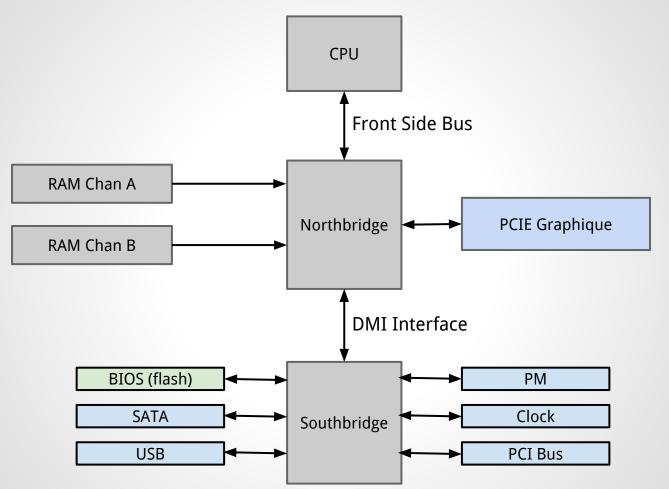

#### **Devices**

- Registers accessible to CPU :

- MMIO

- PIO (in, out)

- Access to Memory (DMA)

- Interrupts (irq, msi)

## What devices are available?

- We need some way to discover devices

- When devices are on a bus there is (usually)

a way to have their description

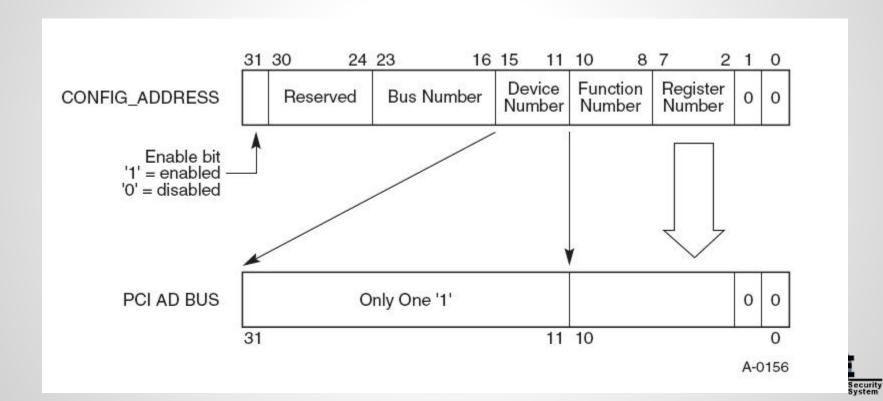

#### **PCI Bus**

- Configuration space accessed through IO Ports

- CONFIG\_ADDRESS (0xcf8)

- CONFIG\_DATA (0xcfc)

## **PCI Address Structure**

# **PCI** Header

| 31 16 15                   |             |               |                |     |

|----------------------------|-------------|---------------|----------------|-----|

| Device ID                  |             | Vendor ID     |                | 00h |

| Status                     |             | Command       |                | 04h |

|                            | Class Code  |               | Revision ID    | 08h |

| BIST                       | Header Type | Lat. Timer    | Cache Line S.  | 0Ch |

| Base Address Registers     |             |               |                | 10h |

|                            |             |               |                | 14h |

|                            |             |               |                | 18h |

|                            |             |               |                | 1Ch |

|                            |             |               | 20h            |     |

|                            |             |               |                | 24h |

| Cardbus CIS Pointer        |             |               | 28h            |     |

| Subsys                     | stem ID     | Subsystem     | Vendor ID      | 2Ch |

| Expansion ROM Base Address |             |               |                | 30h |

| Reserved Cap. Pointe       |             |               | Cap. Pointer   | 34h |

| Reserved                   |             |               |                | 38h |

| Max Lat.                   | Min Gnt.    | Interrupt Pin | Interrupt Line | 3Ch |

## **Serial Port**

- 8250 compatible (or 16550)

- base port on 0x3f8 (for COM1)

- IRQ 4

- ports mapped onto 8250 registers